- 您现在的位置:买卖IC网 > Sheet目录3850 > AT89C51RC2-3CSIM (Atmel)IC 8051 MCU FLASH 32K 40DIP

116

AT89C51RB2/RC2

4180E–8051–10/06

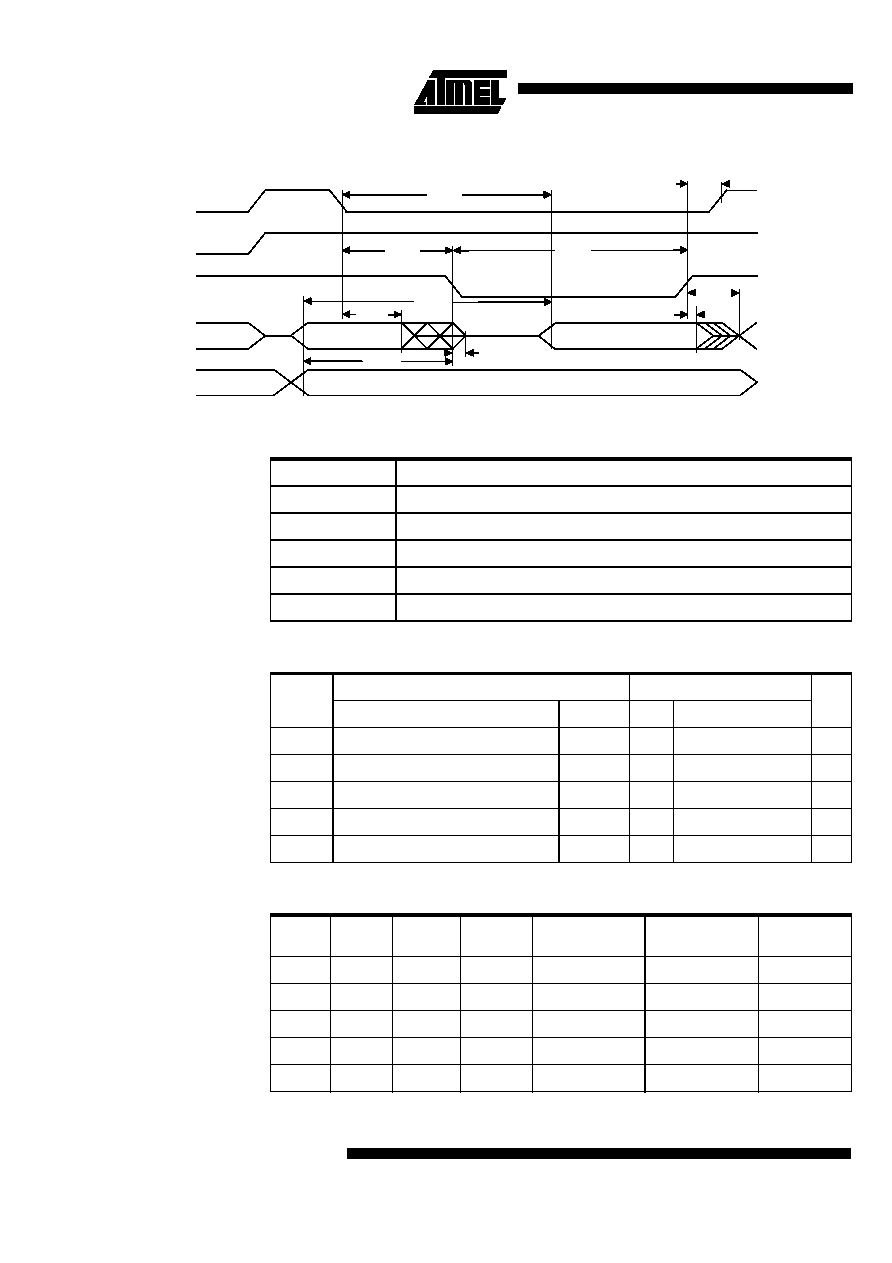

External Data Memory Read Cycle

Serial Port Timing - Shift

Register Mode

Table 80. Symbol Description

Table 81. AC Parameters for a Fix Clock

Table 82. AC Parameters for a Variable Clock

ALE

PSEN

RD

PORT 0

PORT 2

A0-A7

DATA IN

ADDRESS

OR SFR-P2

TAVWL

TLLWL

TRLAZ

ADDRESS A8-A15 OR SFR P2

TRHDZ

TWHLH

TRLRH

TLLDV

TRHDX

TLLAX

TAVDV

Symbol

Parameter

T

XLXL

Serial port clock cycle time

T

QVHX

Output data set-up to clock rising edge

T

XHQX

Output data hold after clock rising edge

T

XHDX

Input data hold after clock rising edge

T

XHDV

Clock rising edge to input data valid

Symbol

-M

-L

Units

Min

Max

Min

Max

TXLXL

300

ns

TQVHX

200

ns

T

XHQX

30

ns

T

XHDX

00

ns

T

XHDV

117

ns

Symbol

Type

Standard

Clock

X2 Clock

X Parameter for -

M Range

X Parameter for -L

Range

Units

TXLXL

Min

12 T

6 T

ns

TQVHX

Min

10 T - x

5 T - x

50

ns

TXHQX

Min

2 T - x

T - x

20

ns

TXHDX

Min

x

0

ns

TXHDV

Max

10 T - x

5 T- x

133

ns

发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

AT89C51RB2-SLSIM

IC 8051 MCU FLASH 16K 44PLCC

AT89C51RB2-SLSIL

IC 8051 MCU FLASH 16K 44PLCC

PIC16C72A-04/SP

IC MCU OTP 2KX14 A/D PWM 28DIP

AT89C51RB2-RLTIM

IC 8051 MCU FLASH 16K 44VQFP

AT89C51RB2-3CSIM

IC 8051 MCU FLASH 16K 40DIP

PIC16C72A-04/SO

IC MCU OTP 2KX14 A/D PWM 28SOIC

AT89C51ID2-RLTIM

IC 8051 MCU FLASH 64K 44VQFP

AT89C51IC2-SLSIL

IC 8051 MCU FLASH 32K 44PLCC

相关代理商/技术参数

AT89C51RC2-3CSUM

功能描述:8位微控制器 -MCU 32kB Flash 1280B RAM 2.7V-5.5V RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

AT89C51RC-24AC

功能描述:8位微控制器 -MCU 32K FLASH 4.0 TO 5.5V - 24MHZ RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

AT89C51RC-24AI

功能描述:8位微控制器 -MCU 32K FLASH 4.0 TO 5.5V - 24MHZ RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

AT89C51RC-24AU

功能描述:8位微控制器 -MCU 32K FLASH 4.0 TO 5.5V RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

AT89C51RC-24JC

功能描述:8位微控制器 -MCU 32K FLASH 4.0 TO 5.5V - 24MHZ RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

AT89C51RC-24JI

功能描述:8位微控制器 -MCU 32K FLASH 4.0 TO 5.5V - 24MHZ RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

AT89C51RC-24JJ

功能描述:8位微控制器 -MCU Microcontroller

RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

AT89C51RC-24JU

功能描述:8位微控制器 -MCU 32K FLASH 4.0 TO 5.5V - 24MHZ 5V RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT